In a technological tour de force, researchers at Stanford University have constructed a one-bit, one-instruction programmable computer on a chip using carbon nanotube-based electronics for all logic elements. Containing 178 carbon nanotube field-effect transistors, the computer is only able to carry out only one instruction, called SUBNEG. However, SUBNEG is Turing-complete, allowing the computer to run, albeit with an extraordinary level of inefficiency, any program, given enough memory, time, and programming ingenuity.

One of the most difficult parts of cramming more computational power into a chip is not based in lithography, but rather in getting rid of the heat associated with the operation of logic elements. Some 15 years ago, the first transistors based upon the physical properties of carbon nanotubes (CNTs) were invented. The essentially perfect atomic-level structure of CNTs makes them excellent conductors of both electricity and heat. Combined with their tiny size (with tube diameters no more than a few nanometers), this makes CNT-based devices a solid candidate to complement, or even supplant, silicon microelectronics technology.

The road to application of CNT-based electronics has been rather slow and filled with challenges. CNTs are essentially narrow sheets of two-dimensional graphene rolled up into a tube. Ideally the edges of the graphene match up so that the tube contains no intrinsic defects. The size and rolling angle of a CNT then determines if it is metallic or semiconducting, with semiconducting bandgaps ranging from 0 eV (metallic) to 2 eV. Their electronic properties are essentially one-dimensional, even though effective electrical contact can be accomplished from electrodes on the CNT's sides.

CNT-based transistors are usually of the field-effect type, in which the conductivity of the nanotube is controlled by the electric field of a gate electrode located between the source and drain of the device. If the electric field of the gate is sufficiently large, electrons cannot pass through the nanotube. Such transistors, however, are only as good as is their geometry: both the geometry of the CNT and the geometry of the device.

Two problems which have plagued application CNT-based applications are the difficulty in controlling the synthesis process to obtain only matched semiconducting CNTs, and the problem of aligning them on a substrate so that misaligned nanotubes do not add unwanted and uncontrolled conduction paths to a circuit. While these problems are not too difficult when constructing one-off circuit elements with nanometer-scale manipulators, the development of potential mass fabrication technologies has been a very difficult road.

This is the main advance accomplished by the Stanford group. They have developed a method to remove metallic and shallow-bandgap semiconducting CNTs by exploding them as if they were tiny electrical fuses. Combined with their recent introduction of a technique for designing circuits that are robust against the sort of uncontrolled wiring errors associated with misaligned CNTs that remain on the surface, they were able to construct a very simple, but general-purpose, von Neumann computer using CNT-based devices. This architecture also allowed them to use off-chip silicon memory with the CNT-based processor, again simplifying the structure of the processor.

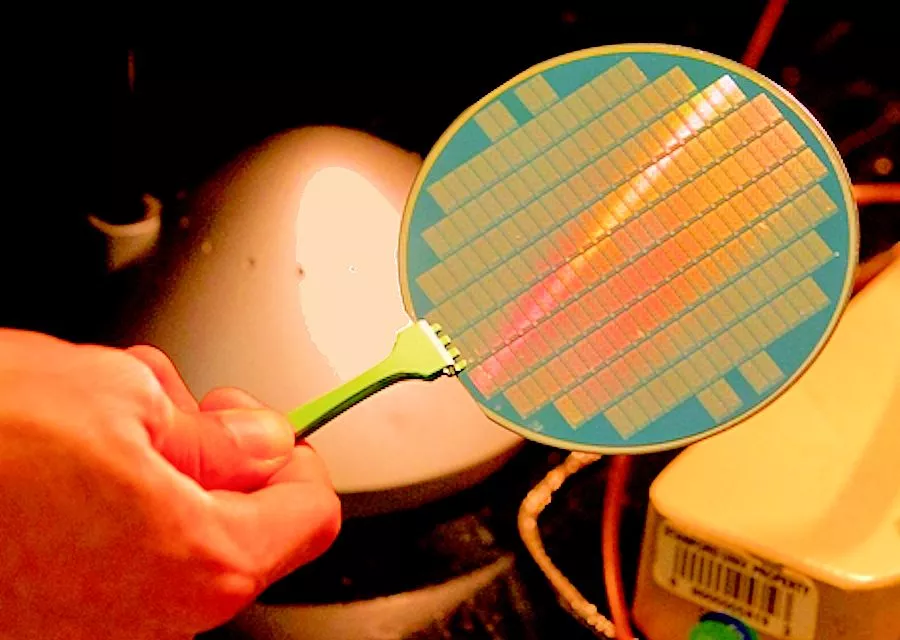

Initially, a layer of CNTs was grown on a quartz substrate using chemical vapor deposition and methane as the source of carbon. Parallel strips of iron were deposited on the quartz surface to act as a template for the growth of the nanotubes. The result was that about 99.5 percent of the nanotubes were properly aligned on the substrate.

The layer of CNTs was then coated with 150 nm of gold. A layer of tape was attached to the top of the gold layer, so that when the tape was removed, the gold layer and the nanotube layer came with it. The tape was adhered to a target silicon wafer on which the processor chips were to be grown. When heated to 125 C (257 F), the adhesive on the tape loses its strength, and can be peeled off while leaving the gold and nanotube layers behind on the substrate. The wafer is cleaned and etched to remove residue from the tape and the gold, leaving behind a highly aligned layer of CNTs.

Electrical contacts and wiring for the CNT-based devices were prepared on the oxidized surface of the silicon wafer prior to transfer of the nanotube layer. Additional contacts are then deposited on atop the nanotube layer, which is patterned and removed where not needed.

The next step is to remove metallic CNTs from the devices. This is necessary to produce functioning devices, as the metallic CNTs would otherwise short out what is intended to be a switching device. To do so, first a bias is applied to the nanotube transistor gate contacts to turn off all conduction through the semiconducting CNTs. This, of course, does not affect the conductivity of the metallic CNTs. Then a large current is pulsed through all the nanotubes, but passes only through the metallic ones, which are oxidized and vaporized as a result. The Stanford researchers were able to apply this current pulse to the entire circuit simultaneously, making this a technique suited for use in large-scale integration.

The yield of the Stanford construction technique is not explicitly stated in the Nature research paper. However, it does state that the typical yield for individual subsystems, such as D-latches, is 80 to 90 percent. They present a block circuit diagram of the processor that suggests there are about 10 such subsystems in the design, which suggests that the yield of working processors is in the neighborhood of 10-30 percent.

To demonstrate the potential of their new design and fabrication methods, the Stanford group has also made a two-bit arithmetic logic unit containing 96 CNT transistors and some 15 stages of cascaded logic.

The new processor has successfully been programmed with a multitasking operating system. This allowed the concurrent execution of a simple counting program and a integer bubble-sort program. In addition, 20 higher-level instructions from the MIPS instruction set, a commonly implemented RISC processor instruction set, were emulated on the new processor to demonstrate that capability.

How in the world does one program a computer that has only one instruction? Recall that a Turing machine can carry out any computation by shuttling back and forth an instruction tape and applying a small set of rules that instruct the tape how to move, and the machine how to alter the tape in response to the current state of the machine.

It turns out that there exist single logical instructions that can be combined with highly convoluted programs to emulate a universal Turing machine. These one instruction set computers have primarily existed as mathematical games or educational examples, although there have been commercial one instruction set computers (e.g. the Dallas Semiconductor MAXQ controllers, which only execute a MOVE command.)

The Stanford group chose to implement the SUBNEG instruction (which stands for SUbtract and Branch if NEGative). This instruction contains two data addresses and a next instruction address that is lacking one significant bit. That bit is computed in response to the subtraction of the data in the first two addresses: if positive the bit is set to zero, and if negative it is set to one. This allows branching between alternate computation paths, which is sufficient to enable the machine to act as a universal computer.

The Stanford CNT processor is clearly nowhere near ready for prime time. The clock speed is 1 kHz, and the restriction to one bit operations using a single instruction would be impractical even at clock speeds a million times faster. It primarily serves as a demonstration of potential, and as such is a major step forward in our attempts to escape the predicted end of the Moore's Law era.

Source: Stanford University